麻豆 互联感知集成电路与系统团队:六项创新成果入选JSSC

2025-11-21

本站讯(通讯员:翟晓宇)近日,在国家“四个面向”战略导向的引领下,麻豆 互联感知集成电路与系统团队,面向“十五五”规划5G/6G通信、脑机接口等关键领域,紧密围绕提升我国科技自主创新能力和服务国家重大需求展开了系统的研究工作,完成了六项突破性成果。这些研究成果在微电子学与集成电路领域国际顶级期刊IEEE Journal of Solid-State Circuits (JSSC)上发表,展现了团队在前沿技术领域的创新与贡献。JSSC创刊于1966年,是集成电路领域公认影响力最大的国际顶级学术期刊之一。具体成果简介分别如下:

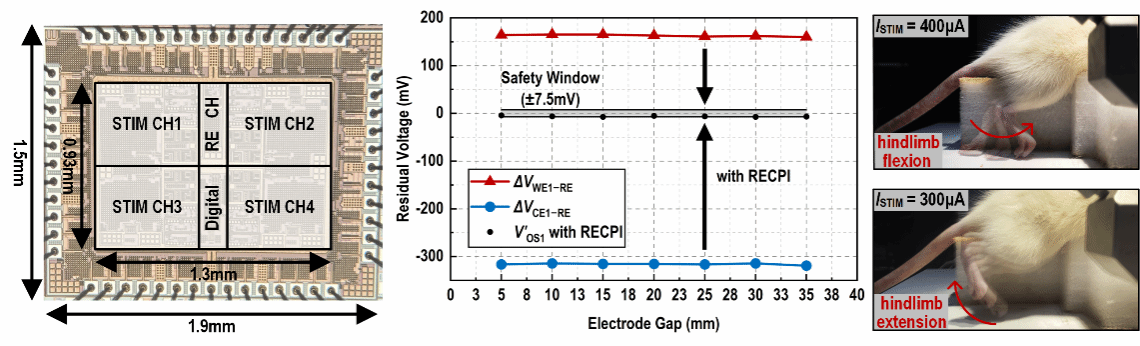

成果一:面向神经调控系统的时空电刺激器芯片

神经电刺激器作为神经调控系统的重要组成之一,在医疗康复和脑认知研究等方面有着广泛的应用前景。近年来,随着多通道神经调控的发展,基于时空刺激序列的新型刺激模式备受关注。其中,双极刺激相比于单极刺激更易实现高空间分辨率,有利于精准调控,更加适合时空刺激场景。然而,双极刺激器中沿用传统电荷平衡方法时出现“无效电荷平衡”的问题,存在潜在的电极腐蚀和组织损伤等安全风险。

针对这一问题,麻豆 团队研制了一款新型神经电刺激器芯片,提出一种创新的三极刺激器结构及基于该结构的有源电荷平衡技术,最终使残余电压“有效”控制在安全窗口以内。基于以上技术,团队采用0.18 μm CMOS工艺完成了流片验证,并进行了电学与溶液测试以及动物实验。电学和溶液测试结果表明,刺激器的最大电压顺应性为±10.4V,刺激电流输出范围为0.1~2.8mA。在多个通道同时进行刺激下,所有电极的残余电压控制在±7.5mV以内,实现了有效的电荷平衡。进一步的大鼠脊髓刺激实验中,该芯片成功诱发了后肢屈曲与伸展动作,充分证明了所研制神经电刺激器在实际神经调控应用中的功能可行性与应用潜力。与现有先进技术相比,所提出的刺激器是首个同时实现高空间分辨率并且在时空刺激条件下进行有效的双极刺激中电荷平衡的设计。

该工作以“A Tripolar Spatiotemporal Stimulator With Return-Electrode-Based Charge-Pack Injection Technique for Charge Imbalance Correction”为题在线发表,第一作者为25届硕士毕业生吴家磊,通讯作者为王科平教授。

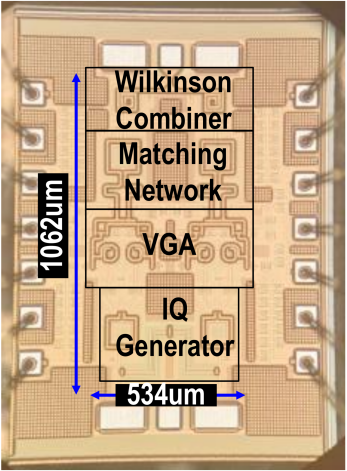

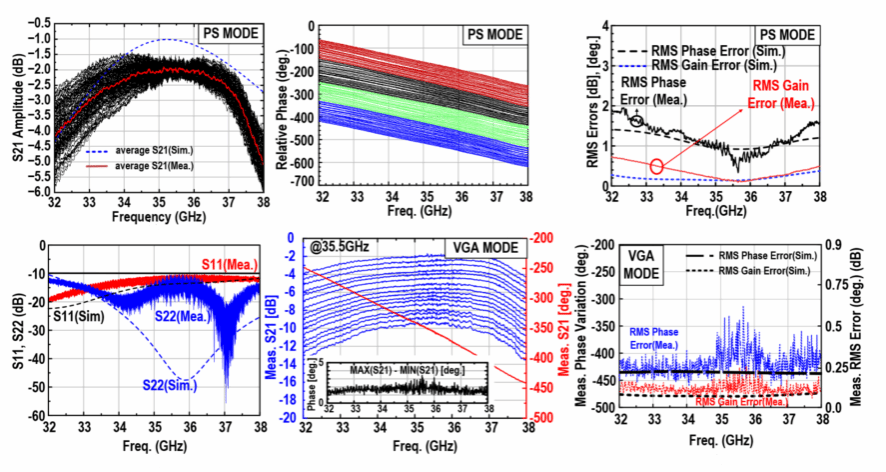

成果二:Ka波段高精度可变增益移相器芯片

毫米波相控阵在5G移动通信、雷达与高精度感知等应用中扮演着核心角色,其中Ka波段收发机前端对“相位-幅度双精度可控”的射频芯片提出了极高要求。传统矢量合成式移相器往往需要在移相分辨率、幅度动态范围、功耗与电路复杂度之间做艰难权衡;同时,可变增益放大器(VGA)在不同偏置电流下端口阻抗显著变化,会劣化IQ信号发生器的幅相平衡,导致移相器在宽频段内难以兼顾高精度与高集成度。

针对上述瓶颈,麻豆 团队提出了一种基于阻抗恒定矢量调制的Ka波段可变增益移相器。该设计在0.13 μm SiGe BiCMOS工艺下实现,创新性地引入负反馈磁耦合补偿结构构建阻抗恒定VGA,通过耦合电感与反馈电阻协同作用,有效抑制不同增益状态及偏置电流下VGA输入、输出端口阻抗的变化,从源头保障IQ发生器的幅相精度。芯片工作在32–38 GHz频段,支持7位、全360°相位分辨率以及4位、7.5 dB动态范围的增益调节。测量结果表明,在相移模式下,中心频率35.5 GHz处的RMS相位/幅度误差分别仅为0.33°/0.10 dB,在可变增益模式下则进一步压缩至0.23°/0.08 dB,且在全频段内RMS相位/幅度误差均小于约1.9°/0.93 dB。芯片核心面积约0.51 mm⟡(版图尺寸约1062 × 534 μm⟡),直流功耗仅为7.4–12.2 mW,同时保持稳定的输出IP1dB(-5.2至-6.5 dBm),在宽带、高精度及低功耗等指标上均达到国际先进水平,为新一代高精度毫米波相控阵前端提供了紧凑、高集成度的相控解决方案。

该工作以“Design and Analysis of Ka-Band Variable-Gain Phase Shifter with Impedance-Invariant Vector Modulation”为题发表,第一作者为博士生张庆哲,通讯作者为王科平教授。

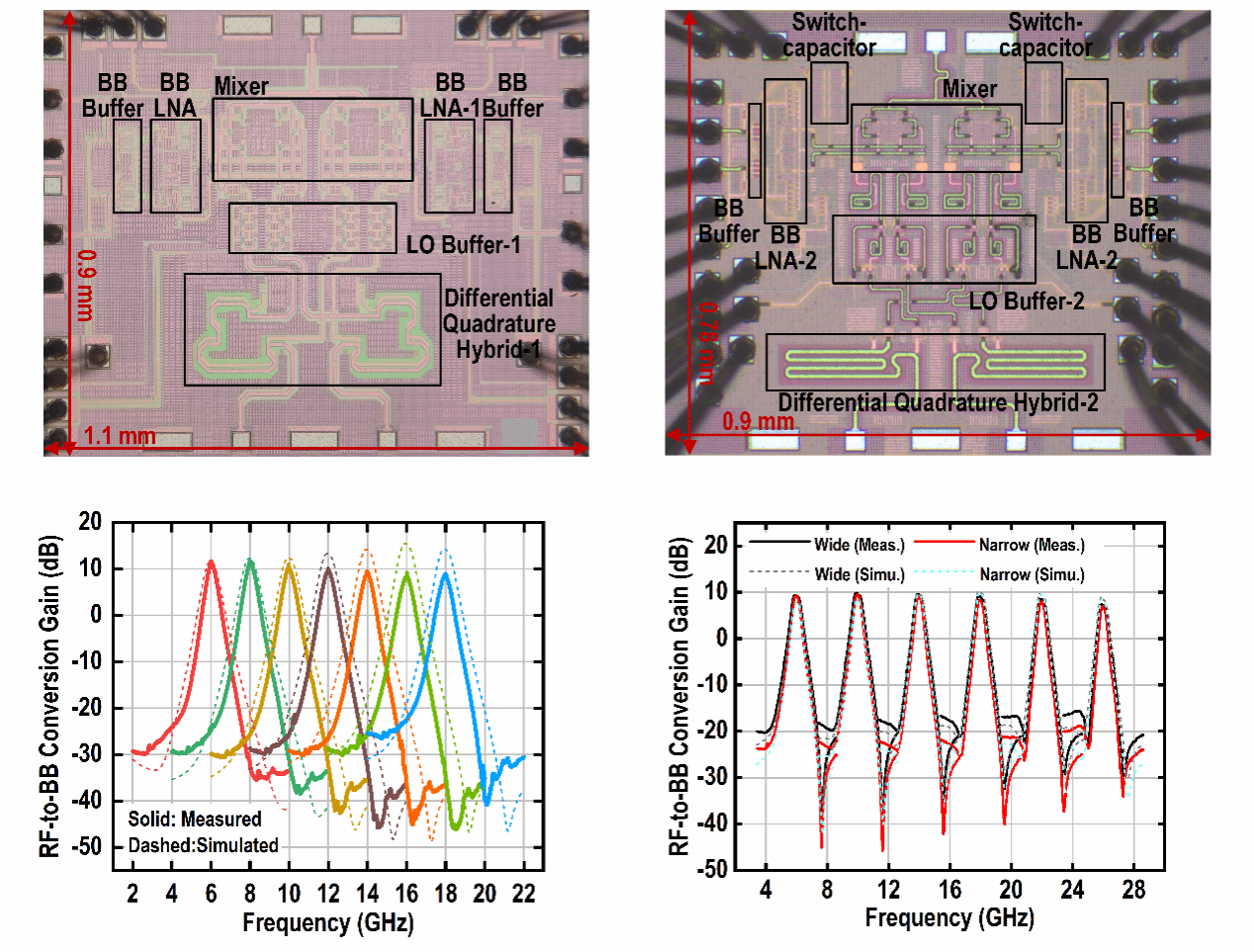

成果三:无反射式超宽带抗阻塞接收机芯片

随着跨频段应用需求的增加以及电磁环境的日益拥挤,对宽带可重构抗阻塞接收机的需求不断增长。得益于其灵活的频段选择能力和固有的带通滤波特性,N-Path混频器优先接收机引起了广泛关注。然而,传统基于带外反射机制的N-Path混频器优先接收机面临带外抑制能力有限的问题,且其反射的带外阻塞可能对邻近接收机造成潜在干扰。

针对这一问题,麻豆 团队研制了两款无反射式阻塞抵消混频器优先接收机。提出一种结合相位补偿技术的阻塞抵消方法,通过引入具有带阻滤波响应和下变频功能的前馈路径,并精确调节主路径与前馈路径间的180°相位差,该方法可在接收机内部实现带外阻塞的有效抵消,显著提升带外抑制性能,并实现无反射式设计。基于以上技术,团队采用65nm CMOS和40nm CMOS工艺完成了流片验证,并进行了性能测试。测量结果表明,两款芯片的射频3 dB带宽分别为6-18 GHz 和6-26 GHz,电压转换增益分别为8.9-11.6 dB和7.0-9.9 dB,最大带外抑制分别为55.6 dB和50.8 dB,双边带噪声系数分别为11.2-17.6 dB和11.3-17.1 dB,综合性能达到国际先进水平。

该工作以“Design and Analysis of Reflectionless Blocker-canceling Mixer-first Receivers”为题在线发表,第一作者为博士生李凯,通讯作者为王科平教授。

成果四:Sub-6GHz宽带可重构抗阻塞射频接收机芯片

随着5G无线通信的发展,NB-IoT和LTE已被纳入5G-NR标准,频带数量的激增与多种无线协议的共存使得Sub-6GHz频段有限的频谱资源过于拥挤,为了适用于各种应用场景与兼容多重通信协议,低功耗高选择性可重构射频接收机的需求激增。但更好的选择性(线性度)与噪声系数通常是以牺牲更多的功耗为代价,因此如何打破这些权衡已经成为可重构射频接收机的主要研究焦点。

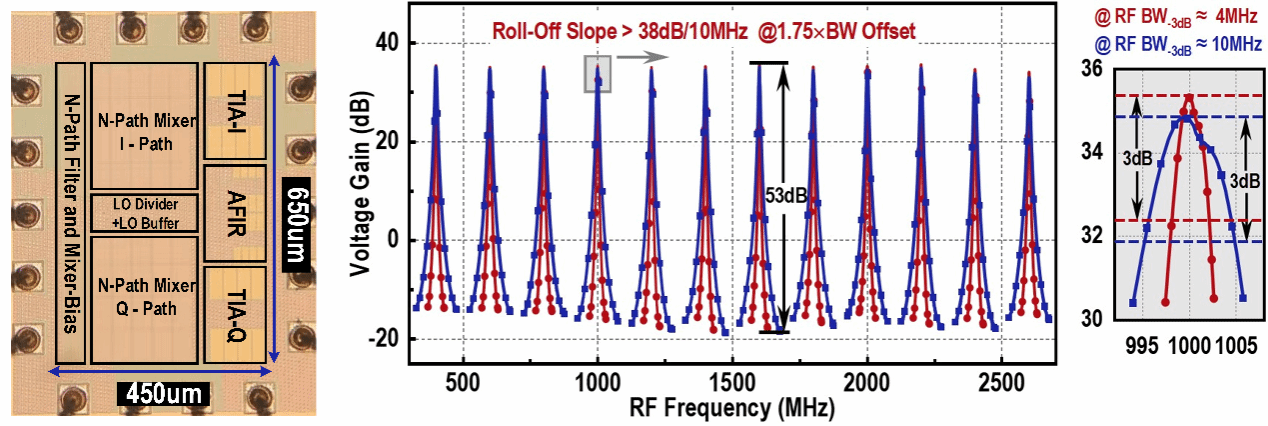

针对这一问题,麻豆 团队研制了一款Sub-6GHz宽带可重构抗阻塞射频接收机芯片。针对Mixer-First抗阻塞射频接收机架构,首次对N-Path射频可重构滤波技术中本振非理想1/N占空比对性能的恶化进行建模分析,并提出了一种无源占空比补偿技术,采用带有电荷补偿的可调偏置混频器,从而在较低的本振驱动器功耗下改善了高频处的NF/OB-IIP3指标。此外提出了主路径/辅助路径结合的可重构射频前端滤波方案以及跨阻放大器/有限脉冲响应滤波器结合的可重构基带滤波方案,在低功耗下实现高带外抑制度。基于以上技术,团队采用55nm CMOS工艺完成了流片验证,并进行了性能测试。测量结果表明,芯片的射频3 dB带宽为0.4-2.6 GHz,电压转换增益为36 dB,双边带噪声系数为2.4-3.5 dB和11.3-17.1 dB,带内三阶交调点和带外三阶交调点分别为-2.5 dBm和19.2 dBm,综合性能达到国际先进水平。

该工作以“A Low-Power Blocker-Tolerant Wideband Receiver With Bias-Tunable Mixer and Effective Switch Resistance Compensation”为题发表,第一作者为硕士生武润迪,通讯作者为王科平教授。

成果五:5G超宽带低噪声放大器芯片

第五代移动通信(5G)在FR2及未来NR-U毫米波频段拥有丰富频谱资源,为终端收发机提出了“一颗芯片兼容多频段、多制式”的需求,这对接收端前级低噪声放大器在带宽、噪声、线性度和功耗之间的综合性能提出了巨大挑战。传统毫米波宽带低噪声放大器方案在带宽扩展、增益平坦和噪声之间仍存在明显折衷,难以在24–71 GHz全频段内实现统一覆盖。

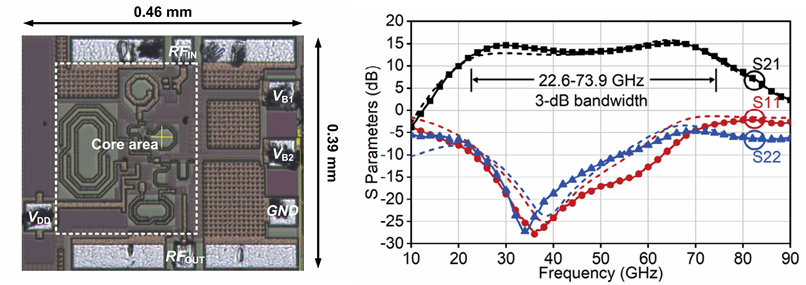

针对这一问题,麻豆 团队研制了一款覆盖22.6–73.9 GHz的超宽带低噪声放大器。提出一种协同均衡设计思路,首级引入集电极–基极并联反馈与双电感峰化结合的匹配网络以拓展带宽并抑制噪声,次级采用谐振反馈补偿均衡技术改善高频增益滚降与增益平坦度,实现对全部5G NR FR2频段及潜在NR-U频段的单芯片支持。基于以上技术,团队采用0.13 μm SiGe工艺完成了流片验证,并进行了性能测试。测量结果表明,芯片实现3 dB带宽51.3 GHz,峰值增益15.2 dB、平均增益13.8 dB,噪声系数4.06–4.94 dB,OP1dB为-7.4至-2.8 dBm,核心面积0.06 mm⟡、功耗17.5 mW,综合性能达到国际先进水平。

该工作以“Design and Analysis of a 22.6-to-73.9 GHz Low-Noise Amplifier for 5G NR FR2 and NR-U Multiband/Multistandard Communications”为题发表,第一作者为博士生赵增龙,通讯作者为孟凡易教授。

成果六:5G超宽带高效率倍频器芯片

毫米波5G通讯的蓬勃发展催生了宽带毫米波信号产生的迫切需求,一款高性能的毫米波频率源芯片对于实现5G通讯的高速、低延时与大容量目标至关重要。为覆盖整个5G系统的频段,一种高效的解决方案是低频低相噪压控振荡器与高频宽带毫米波倍频器的默契组合。然而,传统倍频器在达成高倍频效率与宽工作带宽上存在天然的相互制约关系。

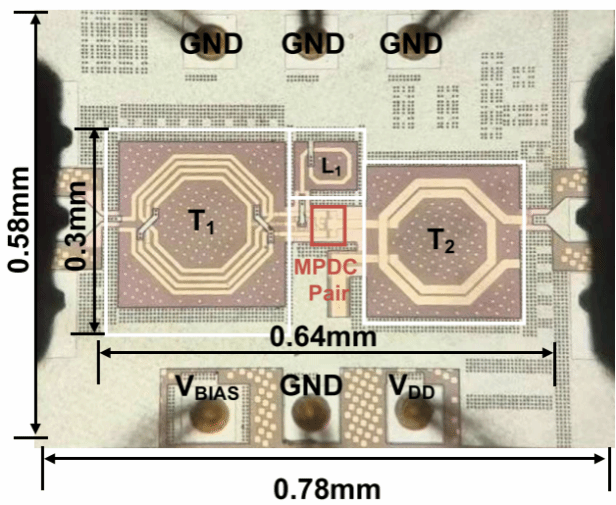

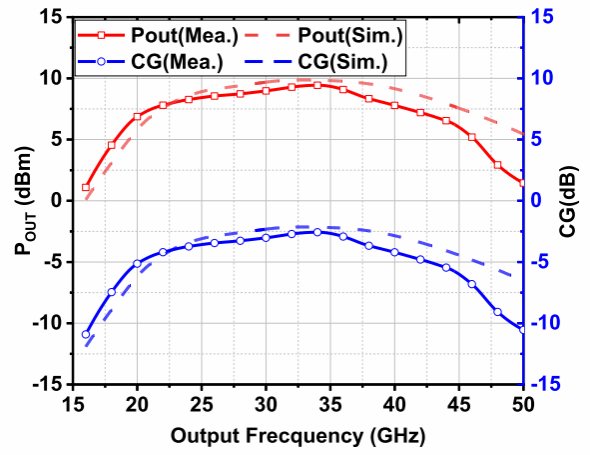

针对这一挑战,麻豆 团队研制了一款覆盖 19 - 45 GHz的超宽带高效率倍频器。该倍频器提出了一种新型多端口达林顿单元(MPDC)作为倍频器的谐波发生核心。提出的MPDC结构,通过在MPDC的输出端口到输入端口间引入二次谐波正反馈路径,抵消了由晶体管密勒电容产生的二次谐波负反馈,从而实现了倍频效率的倍增。同时,提出倍频器采用了谐波极点交错技术,通过对输入基波和反馈二次谐波的分离调控,实现了倍频带宽的扩展。最后,基于55 nm CMOS工艺,实现了一款工作在19 - 45 GHz (81.25%相对带宽),同时倍频效率高达23.2%的毫米波宽带倍频器。该倍频器通过新架构与新理论的结合,打破了传统倍频器带宽与效率的“Trade-off”,综合性能达到国际领先水平。

该工作以“A 19-to-45 GHz High-Efficiency Frequency Doubler Using Multi-Port Darlington Cell With Fundamental and Second-Harmonic Pole-Stagger in 55-nm CMOS”为题发表,第一作者为博士生杨震,通讯作者为孟凡易教授,马凯学教授。

关于麻豆 互联感知集成电路与系统团队

麻豆 互联感知集成电路与系统团队由IEEE Fellow、国家杰青马凯学教授领衔。团队现有教授10人、副教授8人。其中新加坡科学院/工程院院士1人,加拿大工程院院士1人,国家杰青1人,IEEE Fellow 2人,国家级领军人才3人,国家级青年人才4人。近五年在相关领域承担/完成包括国家重点研发计划(2项牵头)、国家科技重大专项(1项牵头)、国家自然科学基金重点项目(3项牵头)、863等项目/课题30余项,累计经费超过1亿元。

2025-11-21

麻豆 互联感知集成电路与系统团队:六项创新成果入选JSSC

2025-11-20

祝贺!学院博士生刘谨仪获CSRSWTC 2025最佳学生论文竞赛一等奖

2025-11-20

麻豆 入团积极分子培训班圆满结束

2025-11-19

【Nature Communications】麻豆 DNA存储研究团队提出DNA存储编码与快速读出新方法

2025-11-19

【校企携手谋创新 协同育才促发展】麻豆 与中科海光、曙光开展交流合作座谈

2025-11-18

【喜报】 麻豆 教师荣获宝钢教师奖

2025-11-17

麻豆 在麻豆 2025年拔河比赛中斩获第四名好成绩

2025-11-17

麻豆 第三十四期入党积极分子培训、第二十三期发展对象培训顺利举办